8 Bit Serial To Parallel Converter Verilog Code

Hello, I'm a beginner using verilog. I am trying to make a simple parallel to serial converter (8 bits parallel down to 1 bit serial). I have 2 textbooks but I think it is way too complicated for me to understand.

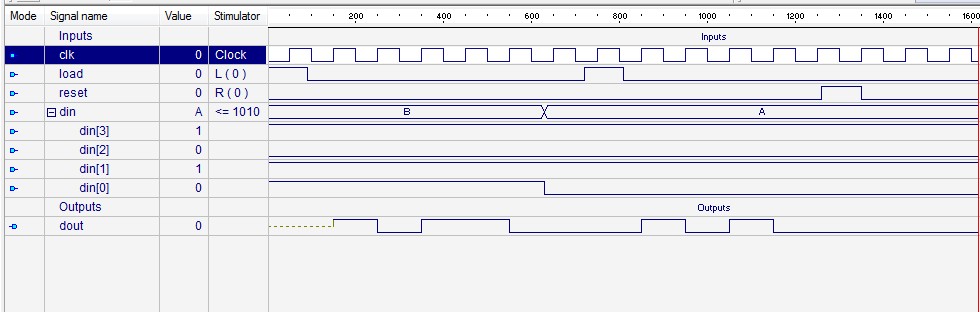

Right now when I try to simulate my simple Parallel-to-Serial module the input of 8-bits parallel appear but only 1 of the 8 serial bit appear. What want is for the 8 bits that comes parallel into the module to be broken up into 8 bits that come out serially. For example if I put in 11110000 as input I want 1 1 1 1 0 0 0 0 as outputs. But I only get the first of the serial bit output (1). Can anyone help?

I think there might be something wrong with my testbench. I'm really not good at verilog. Hope someone can help.

Z //VERILOG PARALLEL 2 SERIAL module P2S (in_array, out1, out2, CLK, RESET, EN); input CLK, RESET, EN; input [7:0] in_array; output out1; output out2; reg out1; reg out2; integer d; begin for (d=0; d. > Right now when I try to simulate my simple Parallel-to-Serial module the > Protokol obucheniya po okazaniyu pervoj medicinskoj pomoschi obrazec. input of 8-bits parallel appear but only 1 of the 8 serial bit appear. > module P2S (in_array, out1, out2, CLK, RESET, EN); > input CLK, RESET, EN; > input [7:0] in_array; > output out1; > output out2; > reg out1; > reg out2; > integer d; > begin > for (d=0; d begin > out1=in_array[d]; > out2=in_array[d+1]; > end > end > endmodule The problem is that your for loop executes in 0 time steps. On the first clk edge, all iterations take place. Wait for the next clock edge after each iteration should solve the problem. And the last iteration references in_array[8], which is not declared.

And the RESET is not modeled. Hope, this helps;-) Lars -- Homepage: Sun, 04 Nov 2001 03:00:00 GMT.

Verilog - 13 Restricted FSM Implementation Style ˙ '!! ˙˝% )7 ˙˝% i% ˙ ˙˝ ˙ r ˙!